# HP 10391B Inverse Assembler Development Package Reference Manual

for the HP 16500A Logic Analysis System, and the HP 1650A/B and HP 1651A/B Logic Analyzers

©Copyright Hewlett-Packard Company 1990

Manual Part Number 10391-90903 Microfiche Part Number 10391-90803

Printed in U.S.A. April 1990

#### **Printing History**

New editions are complete revisions of the manual. Update packages, which are issued between editions, contain additional and replacement pages to be merged into the manual by the customer. The dates on the title page change only when a new edition is published.

A software code may be printed before the date; this indicates the version of the software product at the time the manual or update was issued. Many product updates and fixes do not require manual changes and, conversely, manual corrections may be done without accompanying product changes. Therefore, do not expect a one to one correspondence between product updates and manual updates.

Edition 1 April 1990 10391-90903

#### **List of Effective Pages**

The List of Effective Pages gives the date of the current edition and of any pages changed in updates to that edition. Within the manual, any page changed since the last edition is indicated by printing the date the changes were made on the bottom of the page. If an update is incorporated when a new edition of the manual is printed, the change dates are removed from the bottom of the pages and the new edition date is listed in the Printing History and on the title page.

**Pages**

**Effective Date**

# Product Warranty

This Hewlett-Packard product has a warranty against defects in material and workmanship for a period of 1 year from date of shipment. During warranty period, Hewlett-Packard Company will, at its option, either repair or replace products that prove to be defective.

For warranty service or repair, this product must be returned to a service facility designated by Hewlett-Packard. However, warranty service for products installed by Hewlett-Packard and certain other products designated by Hewlett-Packard will be performed at Buyer's facility at no charge within the Hewlett-Packard service travel area. Outside Hewlett-Packard service travel areas, warranty service will be performed at Buyer's facility only upon Hewlett-Packard's prior agreement and Buyer shall pay Hewlett-Packard's round trip travel expenses.

For products returned to Hewlett-Packard for warranty service, the Buyer shall prepay shipping charges to Hewlett-Packard and Hewlett-Packard shall pay shipping charges to return the product to the Buyer. However, the Buyer shall pay all shipping charges, duties, and taxes for products returned to Hewlett-Packard from another country.

Hewlett-Packard warrants that its software and firmware designated by Hewlett-Packard for use with an instrument will execute its programming instructions when properly installed on that instrument. Hewlett-Packard does not warrant that the operation of the instrument, software, or firmware will be uninterrupted or error-free.

### Limitation of Warranty

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by the Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of the environmental specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. HEWLETT-PACKARD SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

### Exclusive Remedies

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. HEWLETT-PACKARD SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

#### Assistance

Product maintenance agreements and other customer assistance agreements are available for Hewlett-Packard products.

For assistance, contact your nearest Hewlett-Packard Sales and Service Office. Addresses are provided at the back of this operating manual.

#### Certification

Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Bureau of Standards, to the extent allowed by the Bureau's calibration facility, and to the calibration facilities of other International Standards Organization members.

#### Safety

This product has been designed and tested according to International Safety Requirements. To ensure safe operation and to keep the product safe, the information, cautions, and warnings in this operating manual must be heeded.

### **Contents**

| Chapter 1: | General Information Introduction                                                                                                                                                                                       |                                |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|

| -          |                                                                                                                                                                                                                        |                                |  |

|            | Equipment Required                                                                                                                                                                                                     | 1-2                            |  |

|            | Installing the Software                                                                                                                                                                                                |                                |  |

|            | What's On This Disk                                                                                                                                                                                                    | 1-3                            |  |

|            | Installing the Software on a Hard Disk                                                                                                                                                                                 |                                |  |

|            | What the Installation Does                                                                                                                                                                                             |                                |  |

|            | Installing the Software on a Flexible Disk                                                                                                                                                                             |                                |  |

|            | What the Installation Does                                                                                                                                                                                             |                                |  |

|            | Advanced Installation Topics                                                                                                                                                                                           | 1-81-91-111-131-151-161-191-21 |  |

|            | Setting Up the Hardware                                                                                                                                                                                                |                                |  |

|            | Building a Custom Inverse Assembler  Assembling the Source Code  Assembler Options.  Option Definitions  Downloading the Relocatable File  Shortcuts When Using IALDOWN  Batch Files.  Building the Configuration File |                                |  |

|            |                                                                                                                                                                                                                        |                                |  |

|            |                                                                                                                                                                                                                        |                                |  |

|            |                                                                                                                                                                                                                        |                                |  |

|            |                                                                                                                                                                                                                        |                                |  |

|            |                                                                                                                                                                                                                        |                                |  |

|            |                                                                                                                                                                                                                        |                                |  |

|            |                                                                                                                                                                                                                        |                                |  |

|            | Linking the Inverse Assembler and the Configuration File                                                                                                                                                               |                                |  |

|            | Putting It All Together                                                                                                                                                                                                |                                |  |

| Chapter 2: | Inverse Assembler Operation                                                                                                                                                                                            |                                |  |

| Chapter 2. | •                                                                                                                                                                                                                      |                                |  |

|            | Introduction                                                                                                                                                                                                           |                                |  |

|            | Inverse Assembler Operation                                                                                                                                                                                            |                                |  |

|            | Inverse Assembly Process                                                                                                                                                                                               |                                |  |

|            | Summary                                                                                                                                                                                                                | 2-9                            |  |

| Chapter 3: | Writing Inverse Assembler Code                          |      |  |

|------------|---------------------------------------------------------|------|--|

|            | Introduction                                            | 3-1  |  |

|            | IAL Environment                                         |      |  |

|            | The Logic Analyzer Acquisition Memory                   |      |  |

|            | The Accumulator                                         |      |  |

|            | IAL Variables                                           | 3-3  |  |

|            | The Output Display Buffer                               | 3-4  |  |

|            | Developing an Inverse Assembler                         | 3-4  |  |

|            | A Simple Inverse Assembler                              | 3-6  |  |

|            | Reading Acquisition Memory                              | 3-8  |  |

|            | Decoding the STA Instruction                            | 3-8  |  |

|            | Decoding the Destination Address of the STA Instruction | 3-11 |  |

|            | Additional Capabilities of the Input Instruction        | 3-15 |  |

|            | Putting Text into the Output Display Buffer             | 3-17 |  |

|            | Generating Symbolic Addresses                           | 3-18 |  |

|            | Case 1:                                                 |      |  |

|            | Case 2:                                                 |      |  |

|            | Case 3:                                                 |      |  |

|            | Hints on Parsing an Opcode                              |      |  |

|            | Using INPUT_TAG to Mark States                          |      |  |

|            | Other Communication Variables                           |      |  |

|            | RETURN_FLAGS                                            |      |  |

|            | TASK                                                    | 3-23 |  |

| Chapter 4: | Inverse Assembler Instruction Set                       |      |  |

|            | Introduction                                            |      |  |

|            | Choosing a Text Editor                                  |      |  |

|            | Entering Inverse Assembler Source Code                  |      |  |

|            | The First Line                                          |      |  |

|            | Line Format Rules                                       |      |  |

|            | Length of Lines                                         |      |  |

|            | Label Field.                                            |      |  |

|            | Operation Field                                         |      |  |

|            | Operand Field                                           |      |  |

|            | Comment Field                                           |      |  |

|            | Delimiters                                              |      |  |

|            | Numeric Terms                                           |      |  |

|            | String Constants                                        | 4-8  |  |

HP 10391B IAL Development Package Reference Manual

| Language Reference                        |

|-------------------------------------------|

| ABORT 4-9                                 |

| ADD 4-10                                  |

| AND 4-11                                  |

| Pseudo ASCII/ASC4-12                      |

| Pseudo BASE_TITLE                         |

| CALL 4-14                                 |

| CASE_OF 4-15                              |

| COMPLEMENT                                |

| CONSTANT/ CONST Pseudo                    |

| DECREMENT                                 |

| Pseudo DEFAULT_WIDTH 4-20                 |

| EXCLUSIVE_OR4-21                          |

| EXTRACT_BIT                               |

| FETCH_POSITION4-23                        |

| Pseudo FORMAT                             |

| GOTO4-27                                  |

| IF                                        |

| IF_NOT_MAPPED                             |

| INCLUSIVE_OR 4-32                         |

| INCREMENT                                 |

| INPUT 4-34                                |

| Pseudo LABEL_TITLE4-37                    |

| LOAD                                      |

| MAX_INSTRUCTION Pseudo 4-39               |

| NEW_LINE                                  |

| NOP                                       |

| OUTPUT                                    |

| POSITION                                  |

| QUALIFY_MASK & QUALIFY_VALUE Pseudos 4-45 |

| RETURN4-47                                |

| ROTATE 4-48                               |

| SEARCH_LIMIT Pseudo                       |

| SET 4-50                                  |

| STORE                                     |

| SUBTRACT                                  |

| TAG_WITH4-53                              |

| TWOS_COMPLEMENT 4-54                      |

| Pseudo VARIABLE/VAR                       |

**HP 10391B IAL Development Package** Reference Manual

Contents-3

| Appendix A: | 8085 Inverse Assembler                                            |  |  |

|-------------|-------------------------------------------------------------------|--|--|

| Appendix B: | Microprocessors with Incomplete Status                            |  |  |

|             | Introduction                                                      |  |  |

|             | Using INPUT_TAG to Mark States                                    |  |  |

|             | Software Compatibility with other Logic Analyzers                 |  |  |

|             | Synchronizing the Inverse Assembler to the Captured Data B-6      |  |  |

|             | The "Invasm" Field                                                |  |  |

|             | INPUT_TAG Values and How They Change B-8                          |  |  |

|             | Using RETURN_FLAGS B-12 Summary of INPUT_TAGS Bits 16 and 17 B-15 |  |  |

|             | States Containing Multiple Opcodes                                |  |  |

|             | The "Invasm" Field Revisited                                      |  |  |

|             | Code Synchronization with the HP 1630/31 Logic Analyzers B-19     |  |  |

| Appendix C: | 68010 Inverse Assembler                                           |  |  |

| Appendix D: | Assembler Error Messages                                          |  |  |

| Appendix D. | -                                                                 |  |  |

|             | Detection and Listing                                             |  |  |

|             |                                                                   |  |  |

Index

#### Introduction

The HP 10391B Inverse Assembler Development Package allows you to design a custom inverse assembler for the HP 1650A/B, HP 1651A/B, HP 16510A/B, or HP 16511B Logic Analyzers. The inverse assembler runs in the logic analyzer, and converts the "ones and zeros" captured by the analyzer into mnemonics you're familiar with.

The inverse assembler routines are written on an HP Vectra, IBM-PC, or PC compatible using Hewlett-Packard's Inverse Assembly Language. This code is assembled on the PC, then downloaded over RS-232C to the disk in the logic analyzer. The inverse assembler file can then be loaded into a state analyzer to disassemble captured data.

To be successful with this software package, you should be familiar with general programming concepts and simple microprocessor operation. In addition, a basic understanding of state analysis with Hewlett-Packard logic analyzers is assumed in this manual.

This manual is organized as follows:

- Chapter 1 lists the equipment required by this software package, and describes how to install the software on the PC. This chapter also gives a step-by-step guide to using the programs provided in this package. This chapter should be read by all users.

- Chapters 2 and 3 are a tutorial on writing an inverse assembler.

These chapters can be skipped if you've used Hewlett-Packard's Inverse Assembly Language (IAL) on the HP 64000 Development System.

- Chapter 4 is the language reference for the Inverse Assembler Language (IAL).

- The appendices hold listings of sample source code, and a tutorial for advanced topics.

# **Equipment** Required

The following equipment in needed to use the HP Inverse Assembler Development Package:

- 1. HP Vectra, IBM-PC, or PC compatible with a minimum of 256 Kbytes of memory and MS-DOS® 2.1 or above.

- 2. One flexible disk drive with an internal hard disk (recommended configuration) for the PC, or two flexible disk drives.

- 3. RS-232C port configured as COM 1 or 2 on the PC. Recommended card:

- HP 24540A Serial/Parallel Card, or

- HP 24541A Dual Serial Card.

- 4. RS-232C printer cable. Recommended cable:

- For 25-pin ports: HP p/n 13242-60010 or equivalent.

- For 9-pin ports: HP 24542G or equivalent.

- 5. HP 1650A/B or HP 1651A/B Logic Analyzer, or HP 16500A Logic Analysis System with an HP 16510A/B or HP 16511B State/Timing Card installed.

The Inverse Assembler Development Package will require approximately 220 Kbytes of disk space.

# Installing the Software

The Inverse Assembler Development Package includes one 5.25 inch flexible disk which contains all of the software for this package. This section describes how to install this software on a hard disk or another flexible disk.

#### What's On This Disk

The following files are included in the Inverse Assembler Development Package:

| Filename    | Description                                                               |

|-------------|---------------------------------------------------------------------------|

| INSTALL.BAT | Batch file for installing the Inverse Assembler Development Package.      |

| ASM.EXE     | Assembler for HP's Inverse Assembly Language.                             |

| AIAL        | A look-up table used by the IAL assembler.                                |

| IALDOWN.EXE | Download program to put the inverse assembler on the logic analyzer disk. |

| I8085.S     | Source code for Intel 8085 inverse assembler.                             |

| 8085.BAT    | Batch file for automating the assembly and download process.              |

| 8085.CMD    | Input file for use with 8085.BAT                                          |

| I68010.S    | Source code for Motorola 68010 inverse assembler.                         |

| 68010.BAT   | Batch file for automating the assembly and download process.              |

| 68010.CMD   | Input file for use with 68010.BAT.                                        |

# Installing the Software on a Hard Disk

Use the following steps to install the software on a hard disk:

- 1. Insert the 5.25 inch flexible disk containing the HP 10391B software into Drive A: of the PC.

- 2. At the DOS prompt, change the current drive to the hard disk. For instance, if your hard disk is Drive C:, type

C:

at the DOS prompt.

3. At the DOS prompt, make the subdirectory where you want the Inverse Assembler Development Package installed. For instance, if you want to put the software in the subdirectory \ IAL on the hard disk, type

#### MKDIR IAL

at the DOS prompt. If you are installing the software in the root directory or into a subdirectory that already exists, this step is not needed.

4. Change the current DOS directory to the directory where you want the software installed. For instance, if you want to install the software in subdirectory \ IAL, type

#### CD\ IAL

at the DOS prompt.

5. Type

#### A:\ INSTALL

at the DOS prompt. This will begin the installation process. When the installation is completed, you will see the message

#### **Installation Complete!**

on the PC screen and you will be returned to a DOS prompt in the root directory of the current drive.

General Information 1-4

HP 10391B IAL Development Package Reference Manual

### What the Installation Does

Running the INSTALL.BAT batch file does the following:

1. It copies these files from Drive A: to the current directory on the hard disk:

ASM.EXE IALDOWN.EXE

I8085.S 8085.BAT 8085.CMD

I68010.S 68010.BAT 68010.CMD

2. It creates the subdirectory

#### \ HP64700\ TABLES

on your hard disk.

3. It copies the file

#### **AIAL**

into the subdirectory  $\ HP64700\ TABLES$  on your hard disk. This file is a table used by the ASM.EXE program. It MUST be in this subdirectory for the ASM.EXE program to execute properly.

# Installing the Software on a Flexible Disk

Use the following steps to install the software on a flexible disk:

- 1. Insert the 5.25 inch flexible disk containing the HP 10391B into Drive A: of the PC.

- 2. Put the destination flexible disk into Drive B:. If the flexible disk in Drive B: is not formatted, format it at this time.

- 3. At the DOS prompt, change the current drive to Drive B: by typing

B:

at the DOS prompt.

4. At the DOS prompt, make the subdirectory where you want the Inverse Assembler Development Package installed. For instance, if you want to put the software in the subdirectory \ IAL on the flexible disk, type

#### MKDIR IAL

at the DOS prompt. If you are installing the software in the root directory or into a subdirectory that already exists, this step is not needed.

5. Change the current DOS directory to the directory where you want the software installed. For instance, if you want to install the software in subdirectory \ IAL, type

CD\ IAL

at the DOS prompt.

#### A:\ INSTALL

at the DOS prompt. This will begin the installation process. When the installation is completed, you will see the message

#### **Installation Complete!**

on the PC screen and you will be returned to a DOS prompt in the root directory of Drive B:.

#### What the Installation Does

Running the INSTALL.BAT file does the following:

1. Copies these files from Drive A: to the current directory of the flexible disk in Drive B:

ASM.EXE IALDOWN.EXE

I8085.S 8085.BAT 8085.CMD

I68010.S 68010.BAT 68010.CMD

2. Creates the subdirectory

#### \ HP64700\ TABLES

on the flexible disk in Drive B:.

3. Copies the file

#### **AIAL**

into the subdirectory B:\HP64700\TABLES. This file contains a table used by the ASM.EXE program. It MUST be in this subdirectory for the ASM.EXE program to execute properly.

## Advanced Installation Topics

The installation instructions just presented assume you will be executing the ASM.EXE and IALDOWN.EXE files while in the subdirectory where these files are stored. If you want to execute these files while in a different subdirectory, or from a different drive, the following steps will be necessary:

1. Add the PATH statement to your AUTOEXEC.BAT file that points to the subdirectory where the Inverse Assembler Development Package is located. For example, if the software was installed in the subdirectory C:\IAL, you must add the following statement to your AUTOEXEC.BAT file:

#### PATH= C:\ IAL

2. Add the SET statement to your AUTOEXEC.BAT file that points to the drive where subdirectory \ HP64700 was created by the INSTALL.BAT file. For example, if the subdirectory \ HP64700 was created on the C: drive, the following line should be added to your AUTOEXEC.BAT file:

#### SET HPTABLES= C:\ HP64700\ TABLES

After adding these statements to your AUTOEXEC.BAT file, reboot your PC.

These statements will allow you to execute the ASM.EXE and IALDOWN.EXE programs from any subdirectory in your PC.

# Setting Up the Hardware

These steps must be performed to properly set up the hardware for the Inverse Assembler Development Package:

- 1. Connect the logic analyzer to the COM 1 or 2 port of the PC using the RS-232C cable specified earlier in this chapter.

- 2. Turn on and boot up the logic analyzer.

- 3. Check the RS-232C configuration.

- a. If you are using an HP 1650A or HP 1651A, press the I/O key, and select the "RS-232-C Configuration" field.

- b. If you are using an HP 1650B or HP 1651B, press the I/O key, and select "Controller connected to RS-232C."

- c. If you are using an HP 16500A, select the "RS-232C" field in the System Configuration Menu. Change the pop-up to read "RS-232C Connected to: Controller".

- d. The required RS-232C configuration for all of the logic analyzers is:

Protocol: XON/XOFF

Data Bits: 8

Stop Bits: 1

Parity: None

Baud rate: 9600

e. Select the "Done" field on the display when the configuration is set up correctly.

- 4. Set up the logic analyzer disk drive.

- a. Put a blank, unformatted flexible disk into the front disk drive of the logic analyzer.

- b. If you are using an HP 1650A/B or HP 1651A/B, press the I/O key, and select the Disk Operations field.

- c. If you are using an HP 16500A, select the "Configuration" field in the System Configuration Menu. Select the "Front Disk" field to go to the System Front Disk Menu.

- d. Format the blank disk by changing the "Load" field to "Format Disk," then selecting "Execute."

The hardware is now set up to download an inverse assembler from the PC.

#### Building a Custom Inverse Assembler

As an overview, here are the steps needed to build an inverse assembler for an HP 1650A/B, HP 1651A/B, HP 16510A/B, or HP 16511B logic analyzer:

#### 1. Write the inverse assembly algorithm.

The procedures to disassemble the information captured by the logic analyzer are written using HP's Inverse Assembly Language (IAL). The environment, syntax, and constraints of this language are presented in chapters 2 through 4, and appendices A through C of this manual.

The software received with this product includes the source code for the Intel 8085 and Motorola 68010 inverse assemblers. These files may be helpful when first learning the Inverse Assembly Language. Listings of these files are included in appendices A and C.

This source code can be written with almost any PC text editor. For a discussion of the requirements of the text editor, see "Choosing a Text Editor" in chapter 4.

#### 2. Assemble the source code.

The ASM.EXE program included on the software disk is used to convert the ASCII source code written in step 1 into a relocatable file that the logic analyzer can understand.

For a complete discussion of the assembler syntax and options, see "Assembling the Source Code" later in this chapter.

3. Download the relocatable file to the logic analyzer.

The IALDOWN.EXE program copies the relocatable file generated in step 2 to a file on the flexible disk of the logic analyzer. This transfer goes through the RS-232C port configured as COM 1 or 2 on the PC.

IALDOWN.EXE prompts you for the source and destination filenames, the file description, and for the "Invasm" option required. If desired, this process can be automated using a batch file. For all the details on IALDOWN.EXE, see "Downloading the Relocatable File" later in this chapter.

4. Build the logic analyzer configuration file.

The logic analyzer must now be told how to capture information from the target system. This configuration is entered from the analyzer's front panel and must specify the following:

- a. What channels of the logic analyzer are monitoring the address, data, and status information of the target system.

- b. Which clocks are used to latch data from the target system, and which clock edges are used.

If desired, the configuration file can also set up symbol tables and special trace specifications.

Once the logic analyzer configuration is completed, the inverse assembler can be loaded from the logic analyzer disk to disassemble captured states.

For more detail on this step, see "Building the Configuration File" later in this chapter.

The rest of this chapter discusses the details of steps 2, 3, and 4. Writing the source code for an inverse assembler is the topic of chapters 2 through 4, and the appendices of this manual.

General Information 1-12

HP 10391B IAL Development Package Reference Manual

# Assembling the Source Code

The source code for an inverse assembler must be converted into a format that the logic analyzer understands. The ASM.EXE program in this software package is an assembler that does this conversion.

To assemble source code, simply type

#### ASM < filename>

at the DOS prompt, where < filename> is the name of the file in which the source code is stored.

For example, to assemble the source code for the 8085 inverse assembler that was included with this software, type

#### **ASM I8085.S**

at the DOS prompt.

Here is what happens when ASM.EXE is executed:

1. The assembler reads the source code from the file you specified. If it cannot find the file you specified, it will generate the message:

#### asm: Termination, Input source file not found.

2. The assembler then gets a special look-up table from the subdirectory \ HP64700\ TABLES. If the assembler cannot find this file or its subdirectory, it will generate the message:

#### asm: Termination, Unimplemented or invalid processor name

This message indicates that the Inverse Assembler Development package was not installed correctly, or that the line:

#### SET HPTABLES= < disk> \ HP64700\ TABLES

should be added to the PC's AUTOEXEC.BAT file. See the installation section of this chapter for details.

3. The assembler then makes several passes through the source code to convert the source code into a format the logic analyzer can understand. The output of this step is called the relocatable object code, or relocatable code for short.

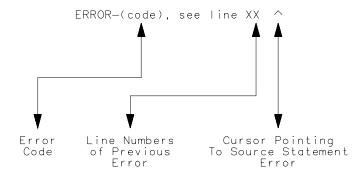

If the assembler encounters any errors in the source code, it will stop the assembly process and generate an error message on the PC screen. A complete list of the assembler error messages is provided in appendix D.

4. Finally, the assembler writes the relocatable code to a DOS file.

The DOS filename is the original filename with ".R" appended to it.

For example, if you typed

#### **ASM I8085.S**

to assemble the 8085 source code, the relocatable code will be placed in the file I8085.R.

For a complete list of the assembler error messages, see appendix D.

# Assembler Options

Options can be specified when calling the assembler to make debugging the source code easier. These options are added to the ASM command when starting the assembly process.

The full syntax of the ASM program is:

$$ASM \ [-o] \ [-l] \ [-n] \ [-e] \ [-x] \ [-t] < file> \ [> list\_file]$$

Items in the square brackets ([..]) are optional parameters for this program.

< file> is the name of the source file to be assembled.

#### **Option Definitions**

ASM recognizes the following options which must be preceded by a dash (-). Options can be concatenated after a single dash (for example, -ox)

- **-o** Generate a listing of the assembler results. This listing includes the following:

- a. Source statements with the associated object code,

- b. Error messages, with a pointer to the error, and

- c. A summary of errors with a descriptive list.

- -l Same as -o

- **-n** No listing of assembler results, except for errors (default).

- **-e** Not implemented for the IAL

- -x Adds a cross-reference to the listing generated by -o or -l.

This cross-reference shows all line numbers that have text in the label field, including variable and constant declarations.

It also shows which lines reference these labels.

- **-t** Causes assembly with no object code generation or relocatable file creation.

For example, ASM -ox I8085.S would assemble the I8085.S file and produce a listing and a cross-reference, as well as the relocatable file I8085.R. The cross-reference is appended to the end of the listing and would begin with:

| FILE: 18085.S |                 | CROSS REFERENCE TABLE |                         |

|---------------|-----------------|-----------------------|-------------------------|

| LINE          | SYMBOL          | TYPE                  | REFERENCES              |

| 231           | LOD_STO         | D                     | 180                     |

| 40            | LO_INPUT_STATUS | Р                     | 644,657,672             |

| 100           | ILLEGAL_OPCODE  | D                     | 196,199,387,417,447,492 |

| 340           | MOVES           | D                     | 336                     |

| 675           | LO_WAS_OPCODE   | D                     | 672                     |

|               |                 |                       |                         |

In the cross-reference table, the letter listed under the TYPE column has the following definition:

A = Absolute

C = Common (COMN)

D = Data (DATA)

E = External

M = Multiple Defined

P = Program(PROG)

R = Predefined Register

S = Special

U = Undefined

The default output location for listings and the cross-references is the PC screen. The listing output can be rerouted to a file using the optional [> list\_file]. For example, the command

#### ASM - ox 18085.S > 18085.L

would do the following:

- 1. Assemble the source code in I8085.S,

- 2. Create a listing of the assembler results, with a cross-reference,

- 3. Put the relocatable code in file I8085.R, and

- 4. Put the listing in file I8085.L.

To dump the listing directly to the PC's printer, use

ASM - ox I8085.S > PRN

# Downloading the Relocatable File

Once the relocatable file has been constructed with the ASM.EXE program, the relocatable file should be downloaded to the disk in the logic analyzer. The download process is handled by the IALDOWN.EXE program.

To start the download, type IALDOWN at the DOS prompt. IALDOWN will do the following:

- 1. Ask you for the filename to store the relocatable file under on the logic analyzer's disk. You should type in the filename after the prompt, then press < Enter> .

- 2. Ask you for the file description that will be displayed in the logic analyzer disk menu. You should type in the file description after the prompt, then press < Enter> .

- 3. Ask you for the name of the relocatable file on the PC. You should type in the name of the relocatable file, including the .R extension, then press < Enter> .

- 4. Ask you which COM Port (1 or 2) you are using. You should type in 1 or 2, depending on which COM Port you are using to download to the HP 1650A/B, 1651A/B, or HP 16500A.

- 5. Ask you for the "Invasm" Field Option. Select the letter for the "Invasm" option that is appropriate for your inverse assembler, then press < Enter> .

The "Invasm" field is used for microprocessors with limited status information. For more information on using this field, see appendix B.

6. When the last question is answered, the program will read the relocatable file from the PC disk and download it through COM 1 or 2 to the front disk of the logic analyzer. It also downloads the filename and file description information. During the download, the logic analyzer will display:

#### STORING FILE TO DISK

7. When the download is complete, the PC will return you to the DOS prompt.

Here are the steps for downloading the 8085 inverse assembler included with this software package. This example assumes the relocatable file is in the same DOS subdirectory as the IALDOWN.EXE program.

C> IALDOWN

Logic Analyzer Filename = 18085

Logic Analyzer File Description (must be 32 characters or less) = INTEL 8085 INVERSE ASSEMBLER

Relocatable File on the PC = 18085.R

COM Port to use (1 or 2)

"Invasm" Field Options:

A = No "Invasm" Field

B = "Invasm" Field with no pop-up

C = "Invasm" Field with pop-up. 2 choices in pop-up.

D = "Invasm" Field with pop-up. 8 choices in pop-up.

Select the appropriate letter (A, B, C or D): A

General Information 1-20

HP 10391B IAL Development Package Reference Manual Some notes on this process:

The logic analyzer filename can be no more than 10 characters long. Valid characters for the filename are A-Z, 0-9, and \_ (underscore). The first character of the filename must be an uppercase alpha character.

The logic analyzer file description must be 32 characters or fewer. Notice that there is a line on the PC screen directly above the file description. This line is 32 characters long and can be used as a "ruler" for your file description.

The relocatable filename must include the .R extension.

## Shortcuts When Using IALDOWN

To save time when using IALDOWN, you may enter the answers to the IALDOWN prompts when starting the program. When answering the IALDOWN questions on the DOS command line, the following rules must be followed:

- 1. Separate each answer by a space,

- 2. Enclose the file description in quotes ("..").

- 3. The logic analyzer filename, the length of the file description, and the relocatable filename extension must follow the guidelines shown in the step-by-step example.

For example, typing

#### IALDOWN I8085 'INTEL 8085 INVERSE ASSEMBLER''18085.R 1 A

at the DOS prompt would download the 8085 inverse assembler through COM 1 to the logic analyzer disk just like the previous step-by-step example.

#### Batch Files

The ASM and IALDOWN programs can be included in batch files to automate the assembly and download process. The files 8085.BAT and 68010.BAT on the software disk are simple examples of batch files for both the Intel 8085 and the Motorola 68010. The 8085.BAT file contains two lines:

#### ASM I8085.S IALDOWN < 8085.CMD

The first line tells the ASM.EXE program to assemble the file I8085.S. The relocatable code will be placed in file I8085.R.

The second line of the batch file starts the IALDOWN program, with the answers to the program prompts coming from file 8085.CMD. 8085.CMD has the following five lines:

I8085 INTEL 8085 INVERSE ASSEMBLER I8085.R

I A

These are the answers to IALDOWN prompts.

To execute this batch file, type

#### 8085

at the DOS prompt. The batch file will then assemble the I8085.S source code and download it to the logic analyzer disk, just like the previous step-by-step example.

If the answers to IALDOWN are placed in a separate file, as shown in this example, each line of the "answer" file must be terminated with a < CR> < LF> (carriage return, line feed).

General Information 1-22

HP 10391B IAL Development Package Reference Manual

# Building the Configuration File

The logic analyzer's configuration file stores the set-up needed by the instrument to capture the states from the target system. A few rules must be followed when configuring the logic analyzer for an inverse assembler to work properly.

- The inverse assembler can only be used in State analysis.

- The following labels MUST be defined in the Format Menu:

| Label | Description                                                                                                                                                               |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR  | Label for the logic analyzer channels connected to the target system Address Bus.                                                                                         |

| DATA  | Label for the logic analyzer channels connected to the target system Data Bus.                                                                                            |

| STAT  | Label for the logic analyzer channels connected to the target system Status Lines. These lines should indicate what kind of bus cycle was captured by the logic analyzer. |

|       | • For the HP 16511B, the following labels must also be defined in the Format menu:                                                                                        |

| Label  | Description                                                                                                   |

|--------|---------------------------------------------------------------------------------------------------------------|

| ADDR_B | Label for the logic analyzer channels connected to the target system auxiliary address bus for the HP 16511B. |

| DATA_B | Label for the logic analyzer channels connected to the target system auxiliary data bus for the HP 16511B.    |

HP 10391B IAL Development Package Reference Manual

General Information 1-23 The ADDR, DATA, ADDR\_B, DATA\_B, and STAT labels are used with specific communication variables in the Inverse Assembly Language. The relationship between the ADDR, DATA, ADDR\_B, DATA\_B, and STAT labels and the communication variables is shown in the table below:

| Label  | Is Linked with the Communication Variable                                                                    |  |

|--------|--------------------------------------------------------------------------------------------------------------|--|

| ADDR   | INITIAL_ADDRESS and INPUT_ADDRESS                                                                            |  |

| DATA   | INITIAL_DATA and INPUT_DATA                                                                                  |  |

| STAT   | INPUT_STATUS                                                                                                 |  |

| ADDR_B | INPUT_ADDR_B                                                                                                 |  |

| DATA_B | INPUT_DATA_B                                                                                                 |  |

|        |                                                                                                              |  |

| Note   | The ADDR_B and DATA_B variables are NOT used in the HP 1650A/B, HP 1651A/B, and HP 16510A/B Logic Analyzers. |  |

Because of the link between the labels and the communication variables, the ADDR, DATA, and STAT labels must be defined in the Format menu before the inverse assembler is loaded from the logic analyzer disk.

The following steps may be used as a checklist when building the logic analyzer configuration file:

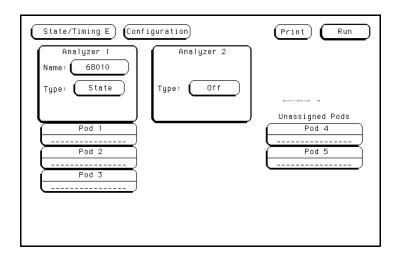

- 1. In the logic analyzer Configuration menu, set up one of the analyzers to be a State Analyzer.

- 2. Assign the pods to the State Analyzer that will capture the signals in the target system. Each pod has 16 channels; assign the number of pods necessary to acquire all of the needed signals.

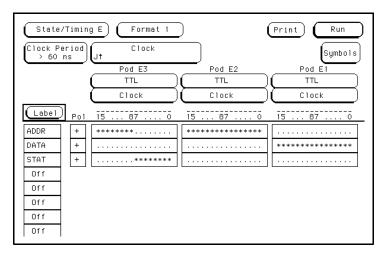

- 3. In the State Format menu, enter the labels ADDR, DATA, and STAT, and labels ADDR\_B and DATA\_B for the HP 16511B. Assign the appropriate channels to each label.

- 4. Set up the clock specification to properly capture states from the target system. The signals captured on the clock edge must be set up 10 ns before the clock edge, and must hold typically 0 ns after the clock edge. Refer to the reference manual for your logic analyzer for exact specifications. Verify the timing of the state clock using timing diagrams for the target system.

- 5. In the logic analyzer Format menu, set the Clock Period field to correspond to how fast you are clocking in data. For more information on the Clock Period field, refer to the reference manual for your logic analyzer.

- 6. If desired, enter additional labels, define Symbol Tables, or set up a Trace Specification for the logic analyzer.

# Linking the Inverse Assembler and the Configuration File

A link can be established between the inverse assembler and the configuration file. With a link established, loading the configuration file from the disk will automatically load the inverse assembler at the same time. Here is how to link the configuration file with the inverse assembler:

- 1. Set up the logic analyzer to capture states from the target system. This can be done manually by entering the configuration from the front panel, or by loading a configuration file from the disk. The configuration must follow the rules listed on page 1-23.

- 2. Insert the inverse assembler disk into the disk drive of the logic analyzer. Load the inverse assembler file from this disk into the analyzer you have configured for state analysis.

- 3. Go to the State Listing.

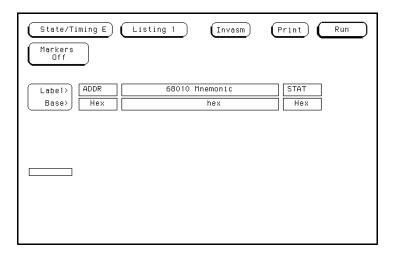

- 4. Go to the field under the DATA label that contains "Hex" and select this field. A pop-up menu will appear on the logic analyzer screen.

- 5. The pop-up will have seven fields. Select the field labeled "Invasm" and the inverse assembler will display mnemonics in place of hex data.

- 6. Store the configuration file to the inverse assembler disk. This establishes a link between the configuration file and the inverse assembler. When the configuration file is loaded it will automatically load the inverse assembler.

# Putting It All Together

This chapter has discussed the steps needed to convert IAL source code to an inverse assembler used with a logic analyzer. This final example will put all the steps together.

In this section, you will actually assemble source code that was provided with the software package and put it on the logic analyzer disk. You will also create the configuration file for this inverse assembler and link the configuration file to inverse assembler. The example used is the inverse assembler for the Motorola 68010 microprocessor.

- 1. If you have not already done so, install the Inverse Assembler Development Package on your PC.

- Connect the hardware as described in this chapter. When finished, you should have a blank, formatted disk in the logic analyzer disk drive.

- 3. Assemble the 68010 source code that was provided with the software package. Type

#### **ASM I68010.S**

at the DOS prompt. This will generate a relocatable file called I68010.R

4. Download the relocatable code to the logic analyzer. Type

#### **IALDOWN**

at the DOS prompt. When prompted by the IALDOWN program, answer the questions as follows:

Logic Analyzer Filename = 168010

Logic Analyzer File Description (must be 32 characters or less) = MOTOROLA 68010 INVERSE ASSEMBLER

Relocatable File on the PC = I68010.R

COM Port to use (1 or 2)

"Invasm" Field Options:

A = No "Invasm" Field

B = "Invasm" Field with no pop-up

C = "Invasm" Field with pop-up. 2 choices in pop-up.

D = "Invasm" Field with pop-up. 8 choices in pop-up.

Select the appropriate letter (A, B, C or D): B

This will download the inverse assembler to the logic analyzer disk. When completed, you will be returned to the DOS prompt on the PC.

5. Manually set up the logic analyzer Configuration and Format menus as shown below.

6. Go to the Front Disk Drive menu and load the inverse assembler into the State analyzer that you just set up.

7. Go to the State Listing menu and change "Hex" under the DATA label to "Invasm." You should see a screen that looks like this:

8. Store the configuration to the logic analyzer disk. Use the filename

C68010

and the description

MOTOROLA 68010 CONFIGURATION

If you want to test this inverse assembler, connect the logic analyzer to a 68000 or 68010 target system using the general purpose probes and grabbers. Connect the signals as follows:

| Signal<br>Name | Logic Analyzer<br>Pod:Bit  | Signal<br>Name | Logic Analyzer<br>Pod:Bit  |

|----------------|----------------------------|----------------|----------------------------|

| A0<br>A1       | Pod 2:Bit 0<br>Pod 2:Bit 1 | D0<br>D1       | Pod 1:Bit 0<br>Pod 1:Bit 1 |

| A1<br>A2       | Pod 2.Bit 1<br>Pod 2:Bit 2 | D1<br>D2       | Pod 1.Bit 1<br>Pod 1:Bit 2 |

| A2<br>A3       | Pod 2:Bit 3                | D2<br>D3       | Pod 1:Bit 2                |

| A4             | Pod 2:Bit 4                | D4             | Pod 1:Bit 4                |

| A5             | Pod 2:Bit 5                | D5             | Pod 1:Bit 5                |

| A6             | Pod 2:Bit 6                | D6             | Pod 1:Bit 6                |

| A7             | Pod 2:Bit 7                | D7             | Pod 1:Bit 7                |

| A8             | Pod 2:Bit 8                | D8             | Pod 1:Bit 8                |

| A9             | Pod 2:Bit 9                | D9             | Pod 1:Bit 9                |

| A10            | Pod 2:Bit 10               | D10            | Pod 1:Bit 10               |

| A11            | Pod 2:Bit 11               | D11            | Pod 1:Bit 11               |

| A12            | Pod 2:Bit 12               | D12            | Pod 1:Bit 12               |

| A13            | Pod 2:Bit 13               | D13            | Pod 1:Bit 13               |

| A14            | Pod 2:Bit 14               | D14            | Pod 1:Bit 14               |

| A15            | Pod 2:Bit 15               | D15            | Pod 1:Bit 15               |

| A16            | Pod 3:Bit 8                | R/W            | Pod 3:Bit 0                |

| A17            | Pod 3:Bit 9                | LDS            | Pod 3:Bit 1                |

| A18            | Pod 3:Bit 10               | UDS            | Pod 3:Bit 2                |

| A19            | Pod 3:Bit 11               | VMA            | Pod 3:Bit 3                |

| A20            | Pod 3:Bit 12               | FC0            | Pod 3:Bit 4                |

| A21            | Pod 3:Bit 13               | FC1            | Pod 3:Bit 5                |

| A22            | Pod 3:Bit 14               | FC2            | Pod 3:Bit 6                |

| A23            | Pod 3:Bit 15               | BGACK          | Pod 3:Bit 7                |

| GND            | Pod 2:Gnd                  | AS             | Pod 1:J Clk                |

| GND            | Pod 3:Gnd                  | GND            | Pod 1:Gnd                  |

Press "RUN" on the logic analyzer to capture bus activity. Under the inverse assembler field, you will see the value of the data bus, plus the kind of bus cycle captured by the logic analyzer.

To see the 68010 mnemonics, do the following:

- 1. Identify a state that you know contains the first state of an opcode fetch.

- 2. Scroll this state to the top line of the screen.

- 3. Select the "Invasm" field at the top of the display.

The inverse assembler will display 68010 mnemonics for the entire screen.

® MS-DOS is a registered trademark of Microsoft Corporation.

**General Information** 1-32

# **Inverse Assembler Operation**

## Introduction

This chapter provides an overview of the inverse assembly process. It explains how the logic analyzer captures data and builds a display, and shows how an inverse assembler fits into this process. It also walks you through the steps needed to properly inverse assemble a microprocessor instruction.

This overview discusses concepts of inverse assembly without going into detail about the actual Inverse Assembly Language syntax. Syntax details are introduced in chapter 3, and a complete language reference is provided in chapter 4.

# Inverse Assembler Operation

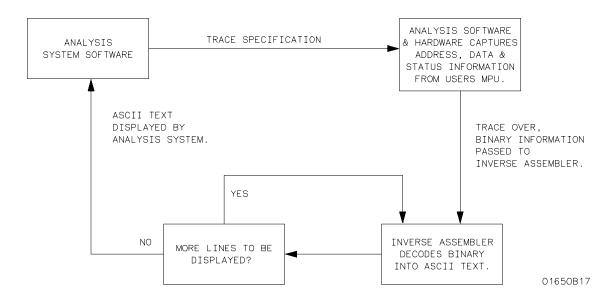

The main function of the inverse assembler is to decode data captured by the logic analyzer. This is done as follows:

- 1. Using the logic analyzer system software, you specify what the logic analyzer should trigger on and what states should be stored. This information is called the "Trace Specification."

- 2. When the "RUN" key is pressed, the system software loads the acquisition hardware with the trace specification, and starts the acquisition. The trace will continue until the trace specification is satisfied or until you stop the acquisition.

- Once the acquisition has stopped, the Address, Data, and Status information captured by the logic analyzer hardware is passed to the system software routines that are used to build the logic analyzer display.

- 4. For each line on the screen, the system software does the following:

- a. Puts the Address information into the Display buffer.

- b. Calls the inverse assembler to convert the captured binary Data information into text. Then it places this text into the Display buffer.

- c. Puts additional labels, including the Status information and the Time count, into the Display buffer.

- 5. The system software displays the contents of the Display buffer and returns control of the instrument to the front panel.

This process is shown in Figure 2-1.

Figure 2-1. How an Inverse Assembler is Used

# Inverse Assembly Process

To show the inverse assembly process, we will use a very simple program for the 8085 microprocessor, shown in example 1.

#### Example 1:

| Location | Object Code | Line     | Source Line |

|----------|-------------|----------|-------------|

|          |             | 1 "8085" |             |

|          |             | 2        | ORG 0100H   |

| 0100     | 32 0601     | 3        | STA 0106H   |

| 0103     | C3 0001     | 4        | JMP 0100H   |

| 0106     | 00          | 5        | NOP         |

During execution, the STA instruction on line 3 stores the contents of the accumulator into the memory location at address 106H. In the next instruction, program control jumps back to STA and the process repeats in a never ending loop.

If the bus cycles generated by this program were captured by a logic analyzer, the display shown in Example 2 would be expected:

Example 2:

| Line # | ADDR<br>Hex | DATA<br>Hex | STAT<br>Bin | Time<br>Rel |

|--------|-------------|-------------|-------------|-------------|

| 0000   | 0100        | 32          | 0011        |             |

| 0001   | 0101        | 06          | 0010        | 2.00 uS     |

| 0002   | 0102        | 01          | 0010        | 1.52 uS     |

| 0003   | 0106        | 00          | 0001        | 1.48 uS     |

| 0004   | 0103        | C3          | 0011        | 1.52 uS     |

| 0005   | 0104        | 00          | 0010        | 2.00 uS     |

| 0006   | 0105        | 01          | 0010        | 1.48 uS     |

| 0007   | 0100        | 32          | 0011        | 1.52 uS     |

| 8000   | 0101        | 06          | 0010        | 2.00 uS     |

| 0009   | 0102        | 01          | 0010        | 1.52 uS     |

| 0010   | 0106        | 00          | 0001        | 1.48 uS     |

|        |             |             |             |             |

etc.

**Inverse Assembler Operation** 2-4

If an 8085 Inverse Assembler was used to interpret the captured information, the following screen would be seen:

### Example 3:

| Line #                                               | ADDR                                                 | 8085 Mnemonic                                                                                 | STAT                                         | Time                                                           |

|------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------|

|                                                      | Hex                                                  | Hex                                                                                           | Bin                                          | Rel                                                            |

| 0000<br>0001<br>0002<br>0003<br>0004<br>0005<br>0006 | 0100<br>0101<br>0102<br>0106<br>0103<br>0104<br>0105 | STA 0106 06 memory read 01 memory read 00 memory write JMP 0100 00 memory read 01 memory read | 0011<br>0010<br>0010<br>0001<br>0001<br>0010 | 2.00 uS<br>1.52 uS<br>1.48 uS<br>1.52 uS<br>2.00 uS<br>1.48 uS |

| 0007                                                 | 0100                                                 | STA 0106                                                                                      | 0011                                         | 1.52 uS                                                        |

| 0008                                                 | 0101                                                 | 06 memory read                                                                                | 0010                                         | 2.00 uS                                                        |

| 0009                                                 | 0102                                                 | 01 memory read                                                                                | 0010                                         | 1.52 uS                                                        |

| 0010                                                 | 0106                                                 | 00 memory write                                                                               | 0001                                         | 1.48 uS                                                        |

etc.

The "8085 Mnemonic" field in Example 3 replaced the "DATA" field in Example 2.

To build the display in Example 3, the system software formats the screen and displays the "Line # " and "ADDR" information. Then the inverse assembler is called to fill in the "8085 Mnemonic" section. Next, the "STAT" and "Time" information is filled in by the system software. This process is repeated for every line on the display.

For the purposes of discussion, we will just look at the STA instruction found in line 3 of Example 1. The 8085 is an 8-bit microprocessor with a 16-bit addressing range. The STA instruction stores the value of the 8-bit accumulator into the memory location specified in the operand field. This instruction gets broken down into the following object code:

| 8-bit opcode | 16-bit address |  |  |

|--------------|----------------|--|--|

| XX           | XXXX           |  |  |

The analysis hardware would have captured the following information when tracing the execution of this instruction:

| State                 | ADDR                                                                                                                                              |                                                                                |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4 | Address of opcode Address of low order address byte Address of high order address byte Address of store (states 2+ 3) Address of next instruction |                                                                                |

| State                 | DATA                                                                                                                                              | STAT                                                                           |

| 0<br>1<br>2<br>3<br>4 | Opcode value Low order address byte High order address byte Accumulator data Next opcode value                                                    | Opcode fetch Operand memory read Operand memory read Memory write Opcode fetch |

In our example, the actual data captured by the analysis hardware follows:

| State | ADDR | DATA | STAT                |

|-------|------|------|---------------------|

| 0     | 0100 | 32   | Opcode fetch        |

| 1     | 0101 | 06   | Operand memory read |

| 2     | 0102 | 01   | Operand memory read |

| 3     | 0106 | 00   | Memory write        |

| 4     | 0103 | C3   | Opcode fetch        |

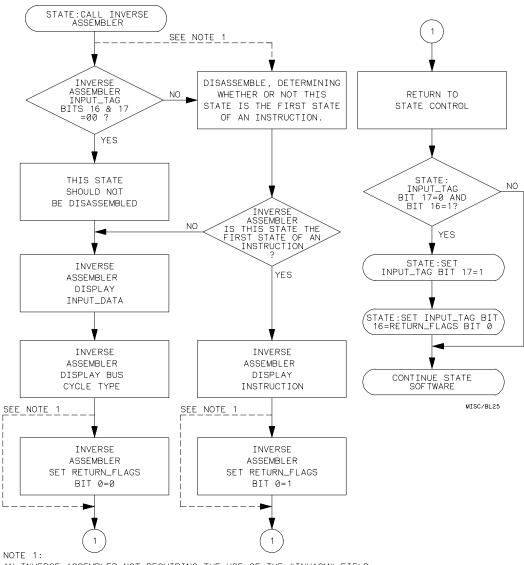

The first step for the inverse assembler is to check the status of the state being disassembled. If the state is an opcode fetch, the inverse assembler should decode it into the appropriate mnemonic. If the state is not an opcode fetch, it should display the captured data and the type of cycle captured.

In this example, the first state captured is an opcode fetch with 32H on the data bus. The inverse assembler should branch to an area of the code that will determine the mnemonic for this opcode. For the 8085, 32H is the object code for the STA instruction, so the inverse assembler will place the following in the output display buffer:

#### **STA**

The 8085 STA instruction is a multi-byte instruction. The two bytes following the opcode indicate the 16-bit address where the contents of the accumulator are to be stored in memory. The inverse assembler must be written to look forward to the next two states to properly decode the destination address of the STA instruction.

The first state following the STA instruction is the lower byte of the destination address; the second state is the upper byte. The inverse assembler will read the data in these two states, combine the results into a single 16-bit quantity and display this address after STA in the display buffer. After doing this, the output display buffer will contain:

#### **STA 0106**

The inverse assembler has now decoded the instruction back into its mnemonic form. Next, it returns to the system software to display the assembly instructions, as follows:

| Line # | ADDR | 8085 Mnemonic | STAT | Time |

|--------|------|---------------|------|------|

|        | Hex  | Hex           | Bin  | Rel  |

| 0000   | 0100 | STA 0106      | 0011 |      |

The inverse assembler will then be called for the next three analysis states that have been used to complete the STA instruction. It checks to see if these states are opcode fetches, and since they are not, the inverse assembler will simply display the status of these states. The first two states after the opcode represent the address of the operand. They are labeled as "read" states. The third state is the result of the STA instruction and is labeled as a "write" operation. Note that the address and mnemonic information show the actual data that was written and the location of the write operation.

| Line # | ADDR<br>Hex | 8085 Mnemonic<br>Hex | STAT<br>Bin | Time<br>Rel |

|--------|-------------|----------------------|-------------|-------------|

| 0000   | 0100        | STA 0106             | 0011        |             |

| 0001   | 0101        | 06 memory read       | 0010        | 2.00 uS     |

| 0002   | 0102        | 01 memory read       | 0010        | 1.52 uS     |

| 0003   | 0106        | 00 memory write      | 0001        | 1.48 uS     |

This completes the task the inverse assembler would normally be expected to perform in displaying the results of the STA instruction execution. The inverse assembler would be called again for the fifth analysis state. In this example, it is the jump (JMP) instruction.

## **Summary**

The following points are the key points of this chapter:

- An inverse assembler is used to convert the data captured by the logic analyzer into text on the logic analyzer display. Often, this text is microprocessor mnemonics.

- The inverse assembler is called once for each state to be displayed on the screen.

- The first thing an inverse assembler should do when called is check the status information for that state. If the status indicates an opcode fetch, the inverse assembler should decode the state into the proper mnemonic. If the state is not an opcode fetch, the inverse assembler should display the captured data and the cycle type.

- When decoding opcode fetches, it may be necessary to look forward in the acquired data to completely decode a multi-byte instruction.

# Writing Inverse Assembler Code

## Introduction

The previous chapter presented on overview of what an inverse assembler is, and what kind of tasks it needs to perform. This chapter will detail how to implement these tasks with Hewlett-Packard's Inverse Assembly Language (IAL).

Inverse assemblers written with the IAL will execute on HP 1650A/B, HP 1651A/B, HP 16510A/B, and HP 16511B Logic Analyzers. The first part of this chapter describes the environment inside the logic analyzer where an inverse assembler executes. The second half of this chapter will discuss some of the IAL instructions that can be used to perform specific inverse assembly tasks.

A complete description of IAL instructions and syntax is provided in chapter 4.

# IAL Environment

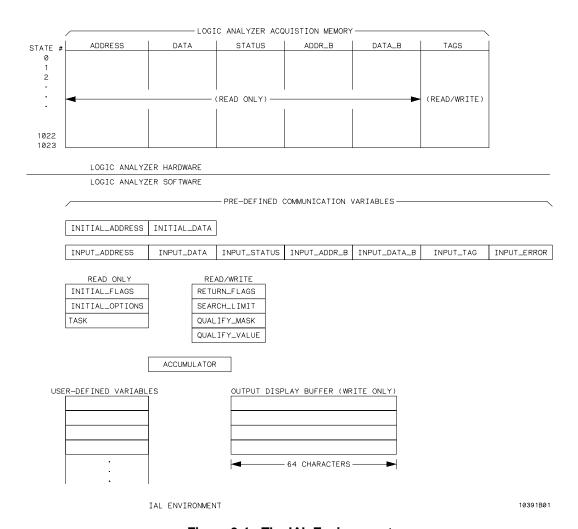

Hewlett-Packard's Inverse Assembly Language defines a simple environment where an inverse assembler is executed. The major elements of this environment are:

- 1. The logic analyzer acquisition memory,

- 2. The ACCUMULATOR,

- Pre-defined communication variables which give the ACCUMULATOR access to the acquisition memory,

- 4. User-defined variables for temporary storage during inverse assembly, and

- 5. The output display buffer.

The logic analyzer acquisition memory is part of the logic analyzer hardware. All other parts of the IAL environment are part of the system software that build up this virtual machine. A block diagram of the environment is shown in figure 3-1 on page 3-5.

HP 10391B IAL Development Package Reference Manual

Writing Inverse Assembler Code

The IAL environment can be thought of as a simple pseudo-processor with a single accumulator. The inverse assembly routine runs on this pseudo-processor. The inverse assembler reads captured information from the acquisition memory, decodes this information into text (such as a microprocessor's mnemonics) and places the text into the output display buffer. As mentioned in the previous chapter, the inverse assembler will be called once for each state to be displayed.

Instructions coded in IAL are executed much like those in assembly language. The instructions are executed one at a time and in sequential order. The GOTO and CALL instructions are used to branch to another area of the inverse assembler. IF and CASE statements can be used for conditional testing.

Similar to simple microprocessor systems, the inverse assembler code is stored in a separate code space. A program counter points to the current instruction being executed by the IAL interpreter. A stack pointer and stack are used in conjunction with subroutine calls. The code space, program counter, stack pointer, and stack cannot be directly accessed by the IAL instructions.

# The Logic Analyzer Acquisition Memory

The logic analyzer's memory is an array of bits that is up to 80 channels wide (160 channels wide on the HP 16511B) and up to 1024 states deep. The channels are grouped under specific labels in the logic analyzer's Format menu: ADDR, DATA, ADDR\_B, DATA\_B, and STAT. These labels are used to identify to the inverse assembler which channels were used for capturing the Address, Data, and Status information for each state captured.

The information captured by the logic analyzer is treated as Read Only Memory by the inverse assembler.

# The Accumulator

The heart of the IAL environment is the ACCUMULATOR. The ACCUMULATOR is a single 32-bit register that can be used for the following:

It can access the logic analyzer acquisition memory through pre-defined communication variables.

Writing Inverse Assembler Code 3-2

- It can read and write variables defined by the user.

- Variables read into the ACCUMULATOR can be written to the output display buffer.

- It can be operated on by arithmetic and logical operations.

- It can be tested using IF and CASE instructions.

Memory-to-memory operations are not supported by the inverse assembly language. To move contents from one variable to another, the contents must first be loaded into the ACCUMULATOR from the source location, then stored to the destination location.

## **IAL Variables**

There are two types of variables used in the inverse assembly language:

- Communication variables provided by the IAL interpreter.

Through these variables, the inverse assembler can read the address, data, and status information captured by the logic analyzer. These variables can also be used to tag states that have already been used for inverse assembly, and can also indicate which captured states contain the first byte of an instruction fetch. Table 3-3 at the end of this chapter lists the communication variables.

- 2. Variables declared by an inverse assembler using the "VAR" pseudo. These can be used for holding temporary values or setting flags for internal use.

All variables and the ACCUMULATOR are treated as 32-bit integers, as shown in the following diagram:

| MSB    | LSB   |

|--------|-------|

| *      | *     |

| Bit 31 | Bit ( |

The ADD and SUBTRACT instructions perform two's complement arithmetic on all variables, which means values can be added and subtracted to get a correct positive or negative result. The highest order bit (31) will be 0 for positive and 1 for negative results. This bit can be tested to see if the value is positive or negative.

All compares done with the "IF" instruction are unsigned. Take care when comparing variables. Since negative numbers will have the most significant bit set in two's complement, the "IF" statement will treat negative numbers as greater than positive numbers. For example, -1 (0FFFFFFFH in two's complement) will be treated as larger than 1 (00000001H in two's complement).

# The Output Display Buffer

The output display buffer is a write-only memory where ASCII text and numbers are written for each state of the inverse assembly display. Each state can print up to four lines with up to 64 characters per line.

# Developing an Inverse Assembler

The development process for an inverse assembler uses the following steps:

- 1. Write the inverse assembler source code.

- 2. Assemble the source code into relocatable code.

- 3. Download the inverse assembler to a logic analyzer disk.

- 4. Load the inverse assembler into the logic analyzer.

- 5. Test and verify the inverse assembler's operation.

This section describes how to write the inverse assembler source code (Step 1 above) that can be properly assembled by the assembler. Steps 2 through 5 are discussed in other sections of this manual. The examples given in this chapter are good examples of the IAL syntax. Refer to chapter 4 for a complete definition of the IAL syntax and instructions.

Writing Inverse Assembler Code 3-4

Figure 3-1. The IAL Environment

# A Simple Inverse Assembler

The source code for a simple, yet complete, inverse assembler is shown below:

- 1 "IAL"

- 2

- 3 OUTPUT "Inverse assembler not present"

- 4 RETURN

If this code were assembled, downloaded to a logic analyzer disk, then loaded into the logic analyzer, typical results would look like:

| Label  | > | ADDR | DATA                          | STAT | Time     |

|--------|---|------|-------------------------------|------|----------|

| Base   | > | Hex  | Invasm                        | Bin  | Rel      |

| + 0000 |   | 0396 | Inverse assembler not present | 0110 |          |

| + 0001 |   | 0397 | Inverse assembler not present | 0110 | 680 nS   |

| + 0002 |   | 6106 | Inverse assembler not present | 1100 | 920 nS   |

| + 0003 |   | 03C5 | Inverse assembler not present | 0110 | 7.24 uS  |

| + 0004 |   | 03C6 | Inverse assembler not present | 0110 | 680 nS   |

| + 0005 |   | 6008 | Inverse assembler not present | 1101 | 920 nS   |

| + 0006 |   | 0396 | Inverse assembler not present | 0110 | 496.6 uS |

| + 0007 |   | 0397 | Inverse assembler not present | 0110 | 680 nS   |

| + 0008 |   | 6006 | Inverse assembler not present | 1100 | 920 nS   |

| + 0009 |   | 03C5 | Inverse assembler not present | 0110 | 7.24 uS  |

| + 0010 |   | 03C6 | Inverse assembler not present | 0110 | 640 nS   |

| + 0011 |   | 6008 | Inverse assembler not present | 1101 | 920 nS   |

| + 0012 |   | 0396 | Inverse assembler not present | 0110 | 524.8 uS |

| + 0013 |   | 0397 | Inverse assembler not present | 0110 | 640 nS   |

| + 0014 |   | 6006 | Inverse assembler not present | 1100 | 920 nS   |

| + 0015 |   | 03C5 | Inverse assembler not present | 0110 | 7.28 uS  |

This screen was generated, starting with line number 0000, as follows:

- 1. The logic analyzer system software displayed the line number of the state and the information captured under the ADDR label.

- 2. The system software called the inverse assembler. In this case, the instruction in line 3 of the source code puts the "Inverse assembler not present" message in the output display buffer.

- 3. When the RETURN instruction was executed in line 4, control was passed back to the system software.